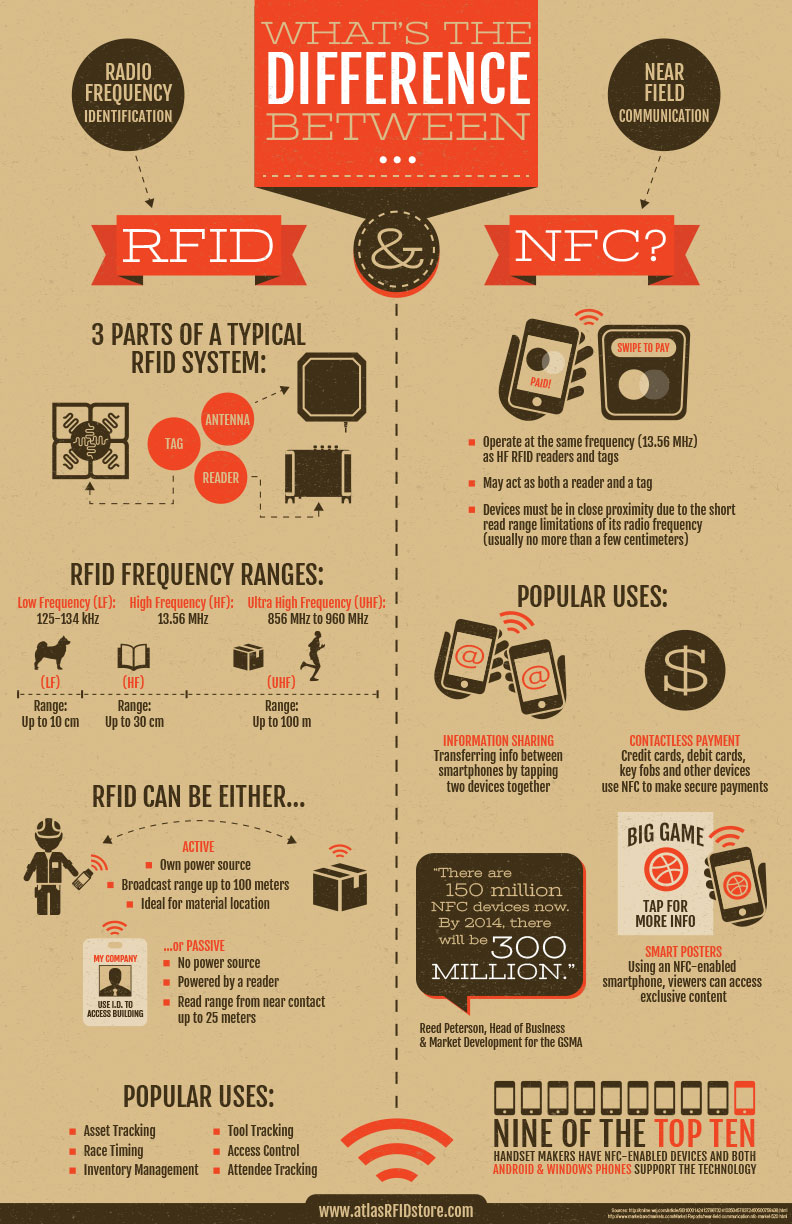

The LM108 op amp is an interesting chip to examine under a microscope because it uses special superbeta transistors for high performance.

Photos of the die reveal the tiny circuitry of the chip as well as unused components that make the chip more complex than necessary.

Surprisingly, these extra components allow the same die to be reused for two totally different chips!

In this article I examine the internals of the LM108 in detail, explain how it works and reveal how the die can take on two roles.

I've written about the famous 741 op amp, which came out in 1968.

A year later, the improved LM108 op amp was invented by eccentric analog IC design genius Bob Widlar.[1]

The main claim to fame of the LM108 is it uses a very small input current, orders of magnitude smaller than the 741.[2]

To attain this low input current, the LM108 contains special transistors called "superbeta" transistors, with about 25 times the amplification of a regular transistor.[3]

The downside is the superbeta transistors are delicate and require special circuitry to protect them from damage.

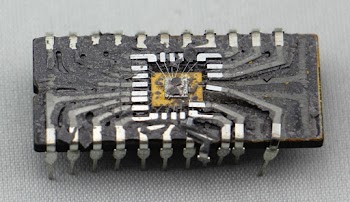

![The LM308 op amp in an 8-pin metal can. The LM308 op amp in an 8-pin metal can.]()

The LM308 op amp in an 8-pin metal can.

The photo above shows the LM108 op amp in a metal can.

(The LM308 is the commercial-grade version of the LM108.[4]

)

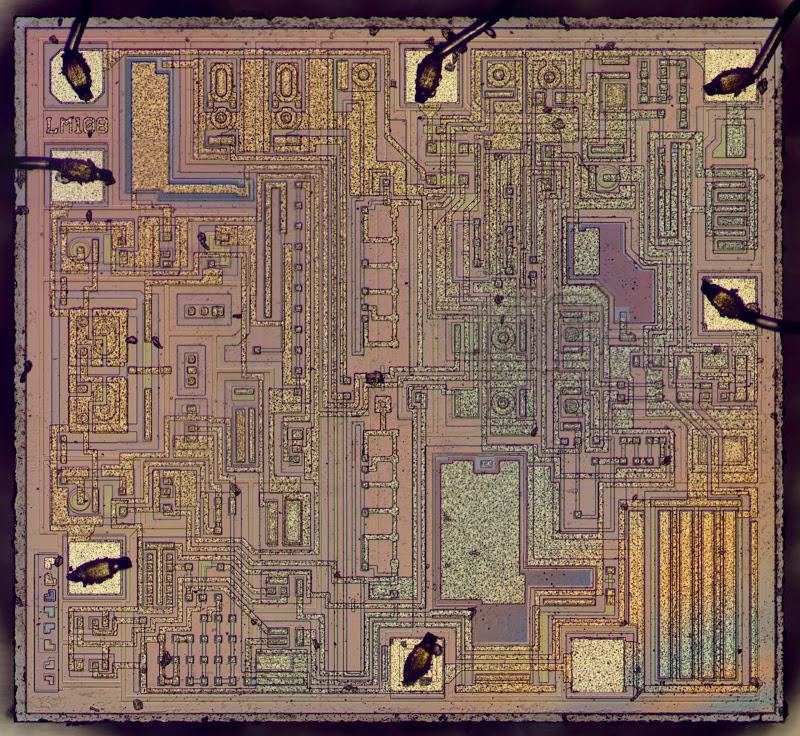

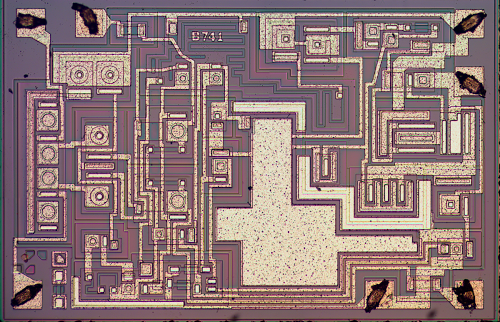

I opened up the can and photographed the die (below).

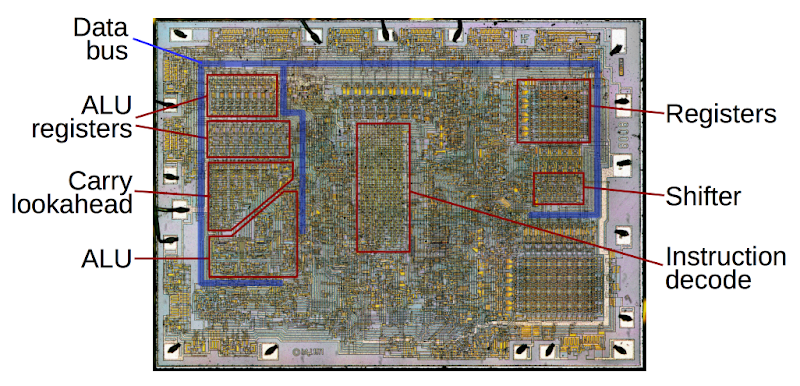

The chip's metal layer is clearly visible, with thin metal traces connecting the different parts of the chip.

The square bonding pads around the edge of the chip are connected by thin wires to the chip's external pins.

Under the metal layer, you can see the silicon that forms the basis of the chip.

To form transistors and resistors,

a process called doping

treats regions of the silicon with elements such as phosphorus or boron.

In the die photo, these regions have a slightly different color, which makes the structure of the chip visible under the metal.

![Die photo of the LM308 op amp. The LM308 is the commercial version of the LM108. Die photo of the LM308 op amp. The LM308 is the commercial version of the LM108.]()

Die photo of the LM308 op amp. The LM308 is the commercial version of the LM108.

While the chip seems incomprehensible at first, close examination reveals the different components and their connections.

By carefully studying the die photo, I reverse engineered the circuit for the op amp.

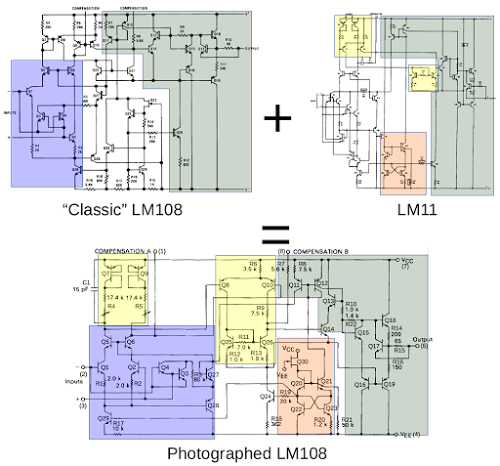

Surprisingly, this chip has an unusual circuit design, more modern than National Semiconductor's "classic" LM108 design.

Although the package has the National Semiconductor logo, the internal circuitry matches the Motorola LM308 datasheet.[5]

You might expect that LM108's would all be the same internally, but as with many ICs, the part number doesn't indicate as much as you expect. Different manufacturers have widely differing implementations of the chip, so you can't expect two chips to behave the same just because they have the same name.[6]

Even so, it's puzzling that a National Semiconductor chip doesn't match the National Semiconductor schematic.

Why op amps are important

The function of an op amp is to take two input voltages, subtract them, multiply the difference by a huge value (100,000 or more), and output the result as a voltage.

If you've studied analog circuits, op amps will be familiar to you, but otherwise this may seem like a bizarre and pointless device. How often do you need to subtract two voltages? And why would you want to amplify by such a huge factor? Would amplifying a 1 volt input result in lightning shooting from the op amp?

It turns out that op amps are extremely useful and versatile, making them a key component in analog circuits.

With simple feedback circuits, you can use an op amp as an amplifier, a filter, integrator, differentiator, or a variety of other circuits.[7] When an op amp is in use, the voltages on the two inputs will normally be almost identical, so multiplying by the huge amplification factor yields a reasonable output of a few volts.

The point of the high amplification is it improves accuracy, even if the amplification of the overall circuit is small.

Transistors inside the IC

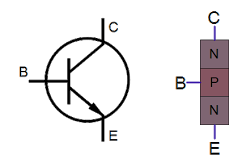

Transistors are the key components in a chip. The LM108 op amp uses NPN and PNP bipolar transistors, while many newer op amps use low-power CMOS transistors instead.

If you've studied electronics, you've probably seen a diagram of an NPN transistor like the one below, showing the collector (C), base (B), and emitter (E) of the transistor. A transistor is usually illustrated as a sandwich of P silicon in between two symmetric layers of N silicon; the N-P-N layers make an NPN transistor.

But it turns out that transistors on a chip look nothing like this, and the base often isn't even in the middle!

![Symbol and oversimplified structure of an NPN transistor. Symbol and oversimplified structure of an NPN transistor.]()

Symbol and oversimplified structure of an NPN transistor.

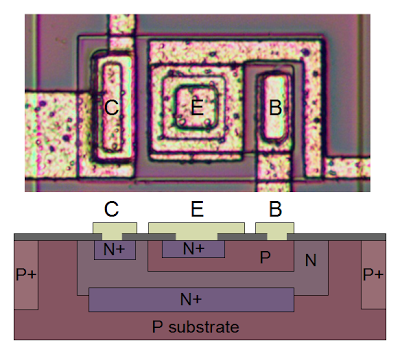

The photo below shows an NPN transistor on a 741 op amp die.

The different brown and purple colors are regions of silicon that has been doped differently, forming N and P regions.

The whitish-yellow areas are the metal layer of the chip on top of the silicon—these form the wires connecting to the collector, emitter, and base.

Underneath the photo is a cross-section drawing showing approximately how the transistor is constructed. There's a lot more than just the N-P-N sandwich, but if you look carefully at the vertical cross section below the 'E', you can find the N-P-N that forms the transistor. The emitter (E) wire is connected to N+ silicon. Below that is a P layer connected to the base contact (B). And below that is an N+ layer connected (indirectly) to the collector (C).

![Structure of an NPN transistor in the 741 op amp Structure of an NPN transistor in the 741 op amp]()

Structure of an NPN transistor in the

741 op amp

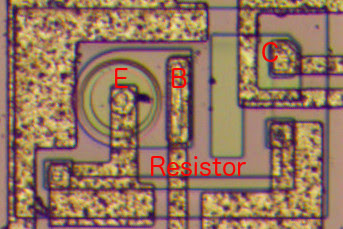

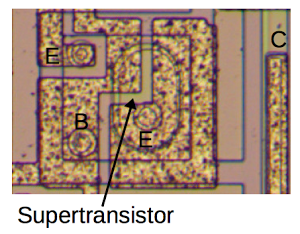

The innovative feature of the LM108 is the superbeta transistor, seen below. It has a much thinner base region below the emitter. This gives the superbeta transistor a much higher beta (i.e. amplification), but makes the transistor much more delicate: just 4 volts between the collector and emitter can "punch through" the thin base and destroy the transistor.

![This image shows one of the superbeta transistors in the LM308 op amp. Note the large, round emitter. The green rectangle below the transistor is a resistor. This image shows one of the superbeta transistors in the LM308 op amp. Note the large, round emitter. The green rectangle below the transistor is a resistor.]()

This image shows one of the superbeta transistors in the LM108 op amp. Note the large, round emitter. The green rectangle below the transistor is a resistor.

How the op amp works

In this section, I'll give a simplified overview of how the op amp works.

[8]

First I'll explain the

differential pair, the important circuit that subtracts and amplifies the two input voltages. The next section explains the different parts of the LM108 op amp.

The final section describes the

current mirror that provides precise currents to the op amp's circuits.

The differential pair

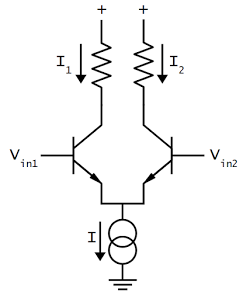

The key component of an op amp is the differential pair, which is the most common two-transistor subcircuit used in analog ICs.

[9]

You may have wondered how the op amp subtracts two voltages since it's not obvious how to make a subtraction circuit. This is the job of the differential pair.

![Schematic of a simple differential pair circuit. The current sink sends a fixed current I through the differential pair. If the two inputs are equal, the current is split equally between the two branches. Otherwise, the branch with the higher input voltage gets most of the current. Schematic of a simple differential pair circuit. The current sink sends a fixed current I through the differential pair. If the two inputs are equal, the current is split equally between the two branches. Otherwise, the branch with the higher input voltage gets most of the current.]()

Schematic of a simple differential pair circuit. The current sink sends a fixed current I through the differential pair. If the two inputs are equal, the current is split equally between the two branches. Otherwise, the branch with the higher input voltage gets most of the current.

The schematic above shows a simple differential pair. The current sink at the bottom provides a fixed current I, which is split between the two input transistors. If the input voltages are equal, the current will be split equally into the two branches (I1 and I2). If one of the input voltages is a bit higher than the other, the corresponding transistor will conduct more current, so one branch gets more current and the other branch gets less.

A small input difference is enough to direct most of the current into the "winning" branch, providing the amplification.

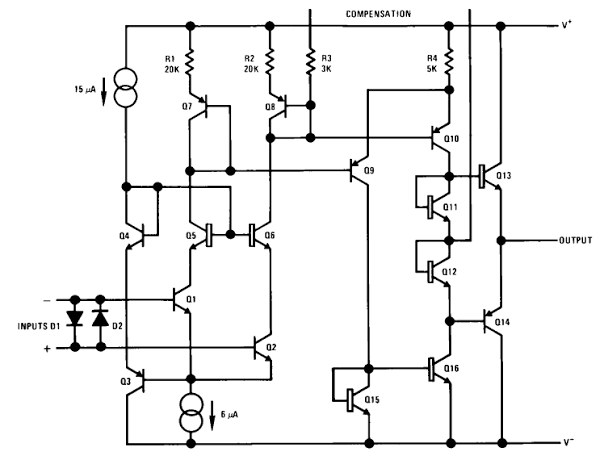

The LM108 op amp circuit

In this section, I'll give a brief explanation of the LM108 circuit, based on

a detailed discussion by Bob Widlar, the chip's designer.

[10]

The schematic below is simplified to show the key features.

The superbeta transistors Q1 and Q2 are the heart of the chip. These form the input stage, and are connected as a differential pair. Resistors R1 and R2 provide the load for the two branches of the differential pair.

By using superbeta transistors for the input, the LM108 achieves high performance with very low input currents.

The problem with superbeta transistors is they will break down and be destroyed by a small voltage difference, just 4 volts.

The LM108 uses a couple interesting circuits to protect the superbeta transistors.

The first protection mechanism is the two diodes across the inputs, ensuring the voltage difference is small. (On the chip, these diodes are implemented with transistors.)

The second protection mechanism is transistors Q5 and Q6, which

ensure that the collector-emitter voltage across the superbeta transistors is essentially zero, preventing an overload. Transistors Q3 and Q4 "bootstrap" the desired voltage from Q1/Q2's emitters to Q5 and Q6.[11]

![Simplified schematic of the LM108 op amp. Simplified schematic of the LM108 op amp.]()

Simplified schematic of the LM108 op amp from the chip's application notes.

[10]

The second stage of amplification is provided by PNP transistors Q9 and Q10.

They form a second differential amplifier that amplifies the output of the first stage.

Instead of resistors, Q15 and Q16 form the load for the second stage differential amplifier.

Transistors Q7 and Q8 bias the inputs of Q9 and Q10 to the right level.

The output of the op amp is driven by a high-current class AB amplifier with power transistors Q13 and Q14. That is, Q13 will pull the output high and Q14 will pull the output low. To ensure that the right output transistor turns on at the right time, Q11 and Q12 bias the output transistors (by two diode drops).

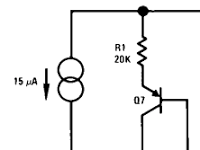

IC component: The current mirror

The schematic above uses a symbol that you may not be familiar with: the double circles that indicate a current source.

A current source may seem like a strange concept, but it is very common in analog integrated circuits.

The idea is that instead of controlling currents with resistors (which are inconveniently large and inaccurate on ICs), currents are generated from a

current mirror.

[12]

Once you have one fixed current, you can use a current mirror to generate copies of this current. Simple modifications can scale the current or even invert it.

![Detail of the LM108 op amp schematic, showing the current source symbol. Detail of the LM108 op amp schematic, showing the current source symbol.]()

Detail of the LM108 op amp schematic, showing the current source symbol.

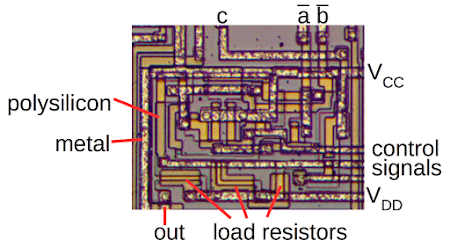

The diagram below shows how a current mirror is implemented.[12] A reference current passes through the transistor on the left. (In this case, the current is set by the resistor.) Since both transistors have the same emitter voltage and base voltage, they source the same current, so the current on the right matches the reference current on the left.

Thus, the current mirror provides a mirror image on the right of the fixed current on the left.

![Current mirror circuit. The current on the right copies the current on the left. Current mirror circuit. The current on the right copies the current on the left.]()

Current mirror circuit. The current on the right copies the current on the left.

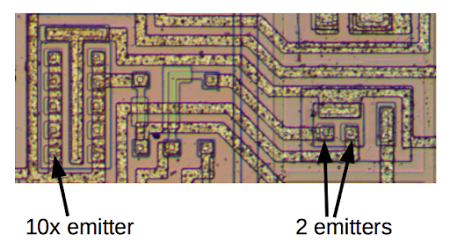

In the LM108, the initial current is generated not by a resistor, but by a

patented four-transistor circuit

that depends on one transistor having 10 times the emitter area of the others.

The photo below shows the transistor that combines 10 square emitters into one large emitter, as well as an unusual transmitter with two separate emitters.[13]

![The LM308's current source contains some interesting transistors. The transistor on the left has 10 emitters wired together, creating a transistor with an effective emitter size of 10 times normal. The transistor on the right has two separate emitters, providing two current outputs. The LM308's current source contains some interesting transistors. The transistor on the left has 10 emitters wired together, creating a transistor with an effective emitter size of 10 times normal. The transistor on the right has two separate emitters, providing two current outputs.]()

The LM108's current source contains some interesting transistors. The transistor on the left has 10 emitters wired together, creating a transistor with an effective emitter size of 10 times normal. The transistor on the right has two separate emitters, providing two current outputs.

Interactive chip viewer

The image and schematic[5] below are an interactive exploration of the LM108. Click a component to see its location on the die and in the schematic highlighted. The box below will give an explanation of the component. The schematic below is the full schematic for the LM108; the component numbers don't match the earlier simplified schematic.

Click components in the image below for more information.

How I photographed the op amp die

Usually getting the die out of an IC requires

concentrated acid to dissolve the epoxy package. But some ICs, such as op amps, are available in metal cans (for shielding) which can be easily opened with a hacksaw

(or even better a jeweler's saw).

I used a

metallurgical microscope for my die photos,

but you can use even a basic middle-school microscope to see many of the chip features.

The photo below shows the LM108 op amp after removing the top. The tiny die is visible in the center, with thin wires connecting the die to the pins that surround it. The metal tab on the right indicates pin 8.

To create the high-resolution die photo, I composited multiple photographs into one image (

details).

![The LM308 op amp has been cut open revealing the tiny die inside. Pads on the die are connected to the pins with thin bond wires. The LM308 op amp has been cut open revealing the tiny die inside. Pads on the die are connected to the pins with thin bond wires.]()

The LM308 op amp has been cut open revealing the tiny die inside. Pads on the die are connected to the pins with thin bond wires.

Some strange things in the LM108 die

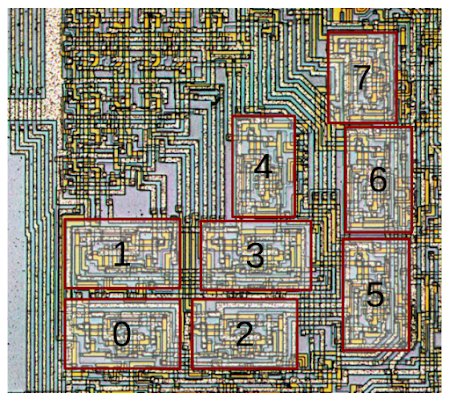

The LM108 die is more complex than I expected and has some strange circuitry.

If you compare the

741 op amp (below) with the LM108, you'll notice that the 741 is much simpler.

Part of this is the LM108 has 30 transistor versus 22 in the 741, but this small increase in components doesn't explain the large increase in the intricacy of the LM108.

After examining the LM108 closely, I realized that it has many components on the die that aren't used.

More investigation revealed that the LM108 die can be reused to create an entirely different op amp, the LM11!

[14]

The manufacturer can use the same die (with a few changes to the metal wiring layer) to produce two different integrated circuits, which presumably saves them money.

![Die photo of the 741 op amp Die photo of the 741 op amp]()

Die photo of the 741 op amp. This chip is much simpler than the LM108.

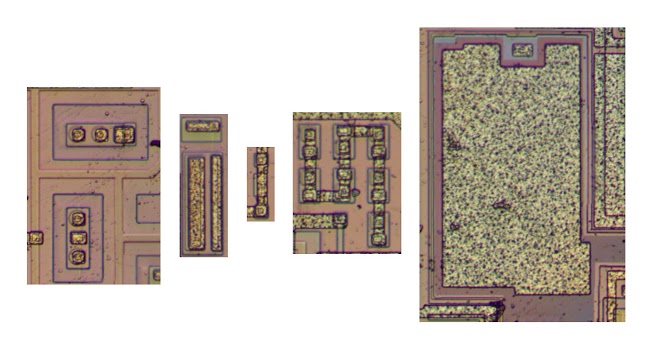

The photo below shows some of the unused components on the LM108 die.

On the left are two unused transistors, including one with two emitters. Next is a larger transistor. The small component is a resistor that is shorted out by the metal on top of it, making it nonfunctional. Seven diodes are connected in an undulating chain, but the chain isn't connected to anything. Finally, the chip has two large unused capacitors, one of which is shown below.

I was puzzled by the amount of space wasted on the die for these unused components.

![The LM308 integrated circuit contains an unusual number of unused components. This image shows some of them: two transistors , a larger transistor, a resistor that is shorted out, a chain of diodes, and a capacitor. The LM308 integrated circuit contains an unusual number of unused components. This image shows some of them: two transistors , a larger transistor, a resistor that is shorted out, a chain of diodes, and a capacitor.]()

The LM108 integrated circuit contains an unusual number of unused components. This image shows some of them: two transistors, a larger transistor, a resistor that is shorted out, a chain of diodes, and a capacitor.

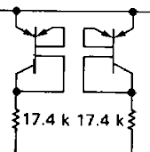

Another puzzle on the LM108 die is it has several resistors that are made up of multiple segments. By shorting out some of these segments with the metal layer, the resistance can be tuned to a desired value.[15]

The mystery is why the LM108 die has so many resistances that need to be customized.

![The LM308 op amp contains several resistors with resistance than can be modified by changing the metal layer. This image shows one resistor with about 20 segments. A few of the segments are shorted out with metal, reducing the resistance. The LM308 op amp contains several resistors with resistance than can be modified by changing the metal layer. This image shows one resistor with about 20 segments. A few of the segments are shorted out with metal, reducing the resistance.]()

The LM108 op amp contains several resistors with resistance than can be modified by changing the metal layer. This image shows one resistor with about 20 segments. A few of the segments are shorted out with metal, reducing the resistance.

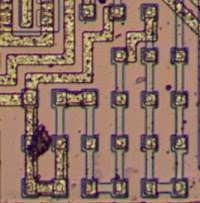

Another strange feature of the LM108 die is the protection transistors are unusually large and have extra unused structures (below).

The transistor has two emitters: one is a regular emitter, and the second is a large, oval superbeta transistor emitter. The superbeta emitter is not wired to anything, which raises the question of why it exists.

The die has other strange, unused transistors.[16]

![This unusual transistor from the LM108 has two emitters: one has a regular base and one has a supertransistor base. The second emitter is not connected to anything. This unusual transistor from the LM108 has two emitters: one has a regular base and one has a supertransistor base. The second emitter is not connected to anything.]()

This unusual transistor from the LM108 has two emitters: one has a regular base and one has a supertransistor base. The second emitter is not connected to anything.

By studying the schematics closely, I think I solved the puzzle of these strange and unused components.

I determined that the LM108 I examined is a combination of the "classic" LM108 and the LM11 op amp introduced in 1980.

The diagram below shows that my chip uses the input stage from the classic LM108 (blue). But the second stage (yellow) and the current source (red) matches the LM11.

All chips use the same output stage (green).

![The LM108 I examined (bottom) is a combination of the 'classic' LM108 and the more modern LM11 op amp. It takes the input stage from the classic (blue) and the second stage (yellow) and the current source (orange) from the LM11. All three op amps use the same output stage (green). The LM108 I examined (bottom) is a combination of the 'classic' LM108 and the more modern LM11 op amp. It takes the input stage from the classic (blue) and the second stage (yellow) and the current source (orange) from the LM11. All three op amps use the same output stage (green).]()

The LM108 I examined (bottom) is a combination of the 'classic' LM108 and the more modern LM11 op amp. It takes the input stage from the classic (blue) and the second stage (yellow) and the current source (orange) from the LM11. All three op amps use the same output stage (green).

My conclusion is the die is designed so it can be used both as an LM11 and an LM108, by just making some changes to the metal layer. Thus, when configured as an LM11, the chip uses the components that are unused in the LM108.

The LM11 schematic shows a zener diode for protection: this is the unused chain of diodes shown earlier.

The LM11 makes use of the other unused resistors, transistors, and capacitors described above.

Finally, the two protection transistors in my LM108 look like a combination of a regular transistor and an unused superbeta transistor. The LM11 schematic shows weird transistors that are half regular and half superbeta, an exact match for these puzzling transistors.

Conclusion

Every IC die has its own interesting puzzles and features, and the LM108 is no exception.

The LM108 is an interesting chip since it uses superbeta transistors for high performance, but requires internal protective circuitry to keep the delicate transistors safe from damage.

The most unusual thing about this LM108 is that the same chip die is used for both the LM108 and the LM11 op amps, just by tweaking the metal layer.

While this makes the die more complex, presumably it saves money for the manufacturer.

Thanks to Bil Herd (famed designer of the Commodore 128) for suggesting the LM108 as an interesting chip to examine. /r/AskElectronics had an informative discussion of the LM108's strange transistors; thanks to crb3 for pointers to relevant documents.

I announce my latest blog posts on Twitter, so follow me at kenshirriff.

Notes and references

[1]

By all reports, Robert Widlar was an amazing analog engineer, as well as an alcoholic crazy guy.

Widlar invented key analog IC circuits such as the

Widlar current source as well as groundbreaking ICs such as the µA702 and µA723. In 1970 he sold his stock options for a million dollars (about 6 million adjusted for inflation) and retired to Mexico at 33.

Some entertaining stories about him are

here, on

Wikipedia, and with

pictures of his sheep.

[2]

The 741 has up to 1.5µA input bias current, while the LM108's maximum input bias current is orders of magnitude lower at 3nA.

[3]

The base of a regular transistor is 0.5 to 1µm thick, while a superbeta transistor has a much thinner base of 0.1 to 0.2µm.

According to an

Application Note

on the LM108, the superbeta transistor has a gain of 5000, compared to 200 for a regular NPN transistor.

The downside is the superbeta transistors have a breakdown voltage of 4 volts, compared to 80 for regular transistors.

[4]

The first digit of the part number specifies the temperature range.

The LM108 is the military-grade chip that can handle the widest temperature range, the LM208 is the industrial-grade chip, and the LM308 is the commercial-grade chip with the narrowest temperature range.

The "H" in LM308AH indicates the metal can package.

[5]

The LM108 schematic that matches my die photo is from

the Motorola LM108 datasheet.

It is strange that my chip is labeled National Semiconductor but its circuit

does not match the National Semiconductor datasheet.

Instead it matches the Motorola datasheet.

Another variant of the LM108 is the Raytheon design (datasheet). This version has a totally different second stage, output stage, and current biasing.

It uses many more transistors: 48 transistors including 6 superbeta devices.

[6]

The LM108 is used in distortion pedals; people search out this op amp to get its specific sound quality when overdriven.

Since different manufacturers have different internal designs for the LM108,

this raises the question of whether people may unexpectedly end up with different op amps that produce different sound effects.

[7]

To see the variety of circuits that can be built from an op amp, see this op amp circuit collection.

The book Op Amp Applications Handbook has a ton of useful information about op amp types (including the LM108), applications, and history; it is also available as a PDF.

[8]

IC Op-Amps Through the Ages.

Op Amp History (Walt Jung) page H.52 (also here) discusses the LM108 in more detail.

[9]

Differential pairs are also called long-tailed pairs.

According to

Analysis and Design of Analog Integrated Circuits

the differential pair is "perhaps the most widely used two-transistor subcircuits in monolithic

analog circuits." (p214)

For more information about differential pairs, see wikipedia, any analog IC book, or chapter 4 of

Designing Analog Chips.

The latter is an excellent book written by Hans Camenzind, the inventor of the 555 timer, so definitely check out the

PDF version.

[10]

Widlar wrote a detailed explanation of the LM108 in IC Op Amp Beats FETs on Input Current (National Semiconductor Application Note 29, Dec 1969).

[11]

To protect the input transistors,

transistors Q3 and Q4 boost the input transistor emitter voltage by two diode drops to make the voltages match.

Transistors Q5 and Q6 are in a cascode configuration.

The result is the collector-base voltage of the input transistors is effectively zero, protecting them.

[12]

A current mirror is a very useful way of connecting transistors so the current through the second transistor matches the current through the first transistor.

For more information about current mirrors, you can check Wikipedia or any analog IC book such as chapter 3 of

Designing Analog Chips.

[13]

The LM108's four-transistor current source is configured so the four base-emitter junctions cancel out, except that one transistor has 10 times the base area of the remainder.

The voltage generated across R20 is kT/q * ln(10), which is approximately 60mV at room temperature, but proportional to absolute temperature.

(The principle of using emitters of different areas is similar to a bandgap voltage reference. However, the bandgap reference is configured so the temperature dependency cancels out and the voltage is stable.)

The resistance of R20 controls the current into the current mirror.

The temperature dependence is used to counteract temperature dependence of other parts of the circuit.

A field-effect transistor (Q30) generates the small current that powers the LM108's current source. The current source circuit turns the unpredictable current from Q30 into a stable output current.

For a full explanation, see patent 3930172.

[14]

The LM11 op amp is discussed in detail in

Reducing DC Errors in Op Amps (National Semiconductor Technical Paper 15) by Widlar.

[15]

In some precision chips, the resistance can be tuned on a per-chip basis, for instance by laser-trimming the resistor or using Zener zapping.

This is not the case in the LM108; the resistances are controlled by the metal layer, which requires a new mask if it is changed.

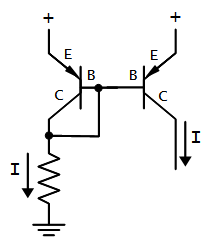

[16]

Two more strange transistors are shown below, with unconnected oval emitters.

![Closeup of two strange transistors on the LM308 die. Closeup of two strange transistors on the LM308 die.]()

Closeup of two strange transistors on the LM108 die.

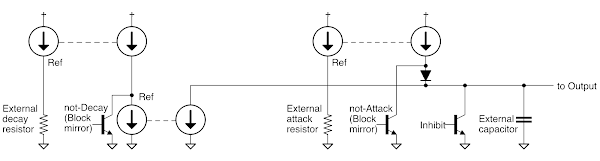

The schematic symbol (below) is even more puzzling, showing transistors with two emitters and two bases. While transistors with two emitters are common in integrated circuits, I've never seen two bases in one transistor.

After discussion on /r/AskElectronics, my theory is the second emitter is tied off on the LM108 but used on the LM11 for the balance inputs.

![Symbol on the schematic for two strange transistors inside the LM108 op amp. Symbol on the schematic for two strange transistors inside the LM108 op amp.]()

Symbol on the schematic for two strange transistors inside the LM108 op amp.